- A frequency or number of cycles per second

- This is normally in Gigahertz (GHz) today

- A hertz (Hz) is one cycle per second.

- But can be slower (MHz, KHz)

- A Typical clock speed is 2GHz

- This is 2x109 cycles per second

- A period or the length of the cycle.

- This is the appropriate units of seconds per cycle.

- A 2GHz clock is 2x109 cycles per second

2GHz = 2x109 cycles per second. Or 1/(2x109) seconds/cycle = 1/2 x 10-9 seconds/cycle = .5 x 10-9 seconds/cycle = 500 x 10-12 seconds/cycle = 500 ps per cycle. = 500 ps/cycle

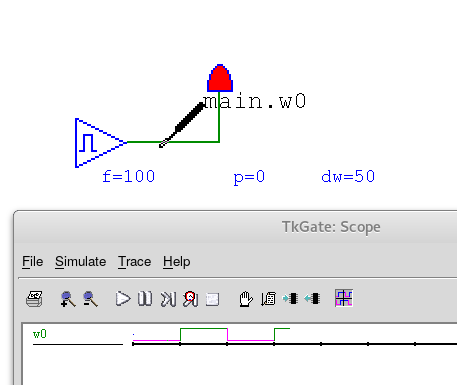

- Clock edges are named.

- When the clock changes from low to high, this is the rising edge or leading edge

- When the clock changes from high to low, this is the falling edge or trailing edge

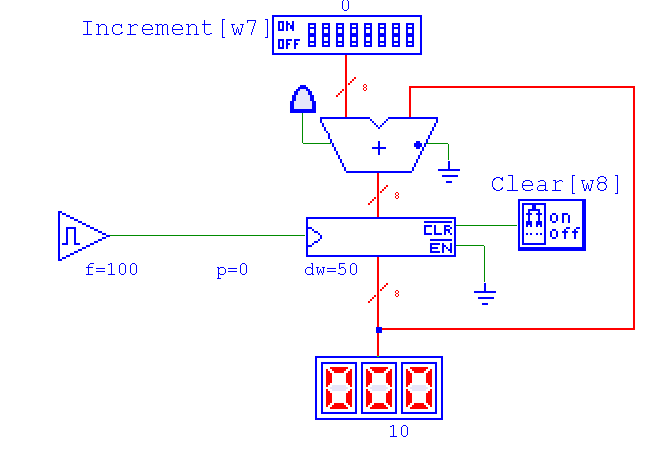

- The following is equivalent to a counter.

- It consists of

- A clock

- A register to hold the current value.

- An adder

- An output display

- An input increment

- A register clear switch

-

- The source is here

- To operate

- Go into simulate mode.

- Set a value on the Increment switch<

- Lower Clear switch for a while (10 time units) until the display is set to 000

- Raise the Clear switch.

- Let the simulation run

- Is the clock cycle length important?

- If we click on the register we find that it wants the clock to be at least 20 ticks long.

- We also find that the Adder is interested in a delta of about 70 ticks.

- So what if we reduced the clock cycle to 50 ticks.

- How is the clock period determined?

- In a CPU with a single cycle clock the entire instruction must be executed in the length of the clock cycle.

- In a CUP with a multi cycle clock instructions are divided into parts and each part of an instruction must be completed in a single clock cycle.

- What?

- Each component of a system has a set amount of time required to perform the assigned operation.

- As we saw, a register in tkgate requires 20 ticks to complete an operation.

- The TKGate Adder produces the carry out in 70 ticks.

- Memory in TKGate requires 80 ticks

- The multiplier requires 124 ticks.

- The divider requires 236 ticks.

- We are looking at things that require additional control, so even though the bus is just a wire, it employs several devices that make it take about 10 ticks

- The CU may take 20 ticks.

- So how long does it take for the fetch phase of every instruction

- BUS ← PC (10 ticks)

- MAR ← BUS (20 ticks)

- MDR ← M[MAR] (70 ticks)

- BUS ← MDR (10 ticks)

- IR ← BUS (20 ticks)

- TOTAL 130 ticks.

- How long will each instruction take?

- Nothing to do here but trace each one through.

- Do you expect these to all be the same length?

- Which would be longest?

- Which would be shortest?

- So what would the problem with a single cycle clock be?

- How long would you make a multiple cycle clock?