$\require{cancel}$

Bus and Tri-State Devices

- This is Carpinelli,

- 4.7 for tri-state buffers

- A bus is a set of wires used to transmit data.

- A single component places data on the bus.

- Multiple components can read the data on the bus.

- It might be better to have direct connections between all components.

- This might eliminate some delays

- But it would require a huge number of wires.

- We need the ability to control access to the bus.

- If two devices transmit at the same time, this would cause problems.

- To do this we use a tri-state buffer.

- In digital, this is called a Driver

- One data input

- One data output

- One control line.

- If the control line is off, there is no output

- If the control line is on, the data is passed from the input line to the output

-

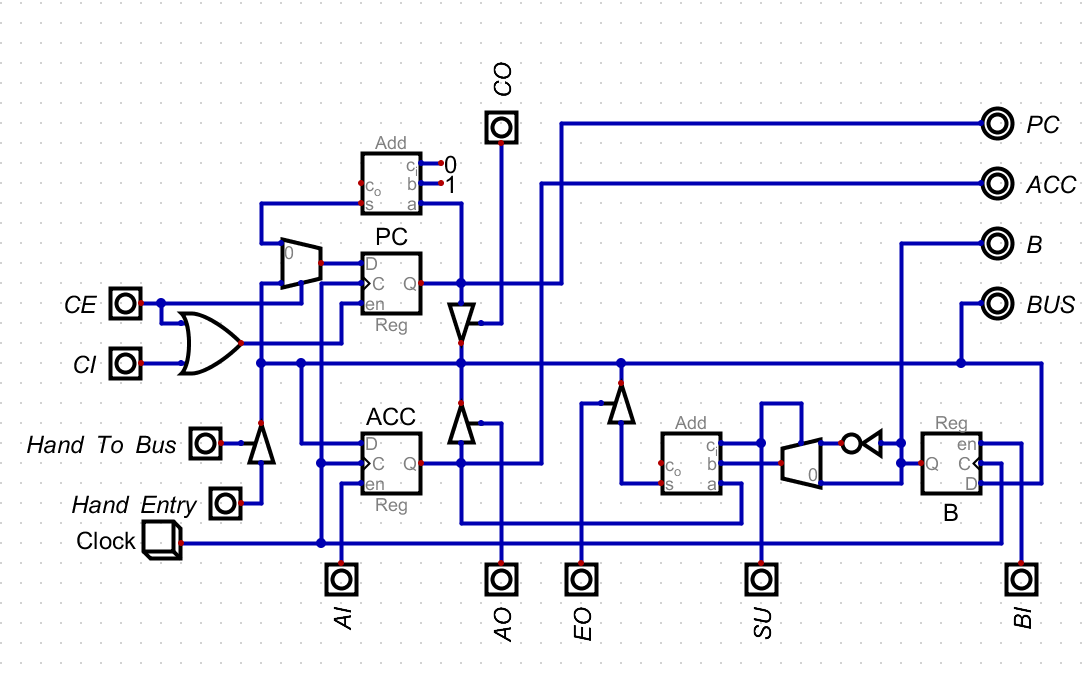

- Consider a partial cpu implementation.

- This circuit is driven by a clock.

- We will try to discuss the clock later if we have time.

- For now, it is the part that drives the registers.

- When the clock changes from low to high, we need to have all input data for the changing register present.

- How would we increment the PC?

- Assert CI

- Pulse the Clock

- Deassert CI

-

jump E

- Put E on the bus by Hand entry, (no IR)

- Assert Hand to Bus

- Assert CE

- Pulse the clock

- Deassert CE

- Deassert Hand To Bus

- Lets do acc=2-3

-

loadi 2

- Put 2 on the bus in Hand entry, (since we don't have an ir)

- Assert Hand To Bus

- Assert AI

- Pulse the Clock

- Deassert AI

- Deassert HandToBus

-

sub F

- Put a 3 on the bus by Hand Entry

- Assert Hand To Bus

- Assert BI

- Pulse the clock

- Deassert BI

- Deassert Hand To Bus

- Assert SU

- Assert EO

- Assert BI

- Pulse the Clock

- Deassert SU, EO, BI