# AN ANIMATED INTRODUCTION TO DIGITAL DI

JOHN D. CARPINELLI

# An Animated Introduction to Digital Logic Design

First Edition

John D. Carpinelli, Ph.D.

Professor, Helen and John C. Hartmann Department of Electrical and Computer Engineering

New Jersey Institute of Technology, Newark, NJ

NJIT Library

New Jersey Institute of Technology

Newark, NJ, USA

#### AN ANIMATED INTRODUCTION TO DIGITAL LOGIC DESIGN

Copyright © 2023 John D. Carpinelli

Published by NJIT Library, University Heights, Newark, NJ 07102

All rights reserved. This book is released as an open textbook under the terms of the Creative Commons license <a href="https://www.creativecommons.org/licenses/">https://www.creativecommons.org/licenses/</a>. <a href="https://www.creativecommons.org/licenses/">https://www.creativecommons.org/licenses/</a>. <a href="https://www.creativecommons.org/licenses/">https://www.creativecommons.org/licenses/</a>.

Under this license, anyone using this open textbook contents herein must provide proper attribution as follows:

- (1) If you would like to redistribute this open textbook in a digital or print format (including but not limited to PDF and HTML), then you must retain this attribution statement on your licensing page.

- (2) If you would like to redistribute part of this open textbook, then you must include citation information including the link to the original document and original license on your licensing page.

For questions concerning this licensing, please contact <u>askalibrarian@njit.edu</u>.

This open textbook is the first publication of the Faculty Authored Open Textbook (FAOT) program, part of NJIT's Open and Affordable Textbook Initiative, and was supported by NJIT's Sabbatical Leave Award. To learn more about NJIT's Open and Affordable Textbook Program, visit <a href="https://researchguides.njit.edu/opentextbooks/">https://researchguides.njit.edu/opentextbooks/</a>.

Book cover image by John D. Carpinelli

Book cover design by Ann D. Hoang

First electronic edition 2023. https://digitalcommons.njit.edu/oat/1/.

ISBN: 978-1-970194-005 (eBook)

DOI: https://doi.org/10.60826/kr55-0k56

# To Mary, Maria, and Tony, and Mom and Dad

## **About the Author**

John D. Carpinelli, Ph.D. is a Professor of Electrical and Computer Engineering in the Helen and John C. Hartmann Department of Electrical and Computer Engineering at the New Jersey Institute of Technology. He holds a Bachelor of Engineering from Stevens Institute of Technology, a Master of Engineering, and a Ph.D. from Rensselaer Polytechnic Institute.

His research interests focus on engineering and STEM education and computer architecture. He has received several awards for his educational service and has been designated a Master Teacher at NJIT.

## **Use of Open Textbook Request**

This book is released as an open textbook under the terms of the Creative Commons license <u>Attribution-NonCommercial-ShareAlike 4.0 International (CC-BY-NC-SA 4.0)</u> except where otherwise noted. In short, you are free to share and adapt this material for non-commercial purposes with appropriate attribution. The full version of this license is available at <a href="https://www.creativecommons.org/licenses/">https://www.creativecommons.org/licenses/</a>.

There is no cost for students and instructors, or anyone, to use this book, either in a formal course or for self-study. If you find this book useful, I encourage you to consider "paying" for it by doing something to help others. Possibilities include a monetary donation to a charity, if your means permit, donating time to a worthy cause, working on a community outreach activity with a campus group, or any other way you can imagine. This is completely optional, and you're welcome to use this book whether or not you choose to do this. To be clear, do not send any money to me personally. I want to state explicitly that I am not asking for, and I will not accept any donations. There are many deserving organizations that would benefit from your assistance.

John Carpinelli

## **Preface**

This book is designed for use in an introductory course on digital logic design, typically offered in computer engineering, electrical engineering, computer science, and other related programs. Such a course is usually offered at the sophomore level. This book makes extensive use of animation to illustrate the flow of data within a digital system and to step through some of the procedures used to design and optimize digital circuits.

#### My Approach

There are numerous textbooks available that focus on digital logic design, and many of them are quite good. Any printed book, however, is limited in how it can present information. From its inception, I wanted to do something different with this book. Publishing this solely as an electronic book (eBook), I wanted to take advantage of the medium to present material in a way that I could not do in a traditional printed book. For this reason, this book incorporates animation to illustrate the functioning and flow of data within circuits throughout the book.

Over the past few years, I have perceived a shift in the learning styles of my undergraduate students. I believe that more of my students now are visual learners than in my earlier years in academia. The animations are an attempt to address this change and improve student learning.

The animations vary widely in complexity, ranging from showing all possible inputs and outputs of an AND gate to stepping through a function minimization using the Quine-McCluskey algorithm to showing the timing of data values changing within a sequential circuit. The animations are not very fancy; they are meant to convey knowledge with a minimum of distractions. Pixar certainly receives no competition from the animations in this book.

I like to include a lot of design work in my courses. I believe this helps students attain a deeper understanding of the material. For this reason, this book contains numerous design examples to illustrate circuit functions and design methodologies. The end-of-chapter problems are also weighted heavily toward design.

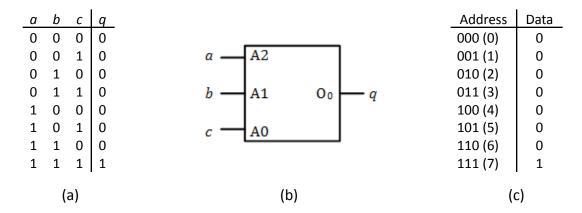

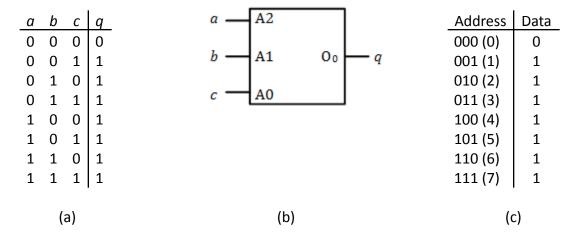

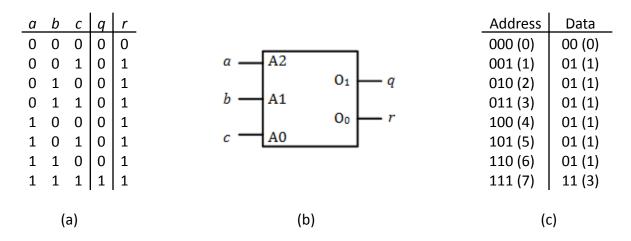

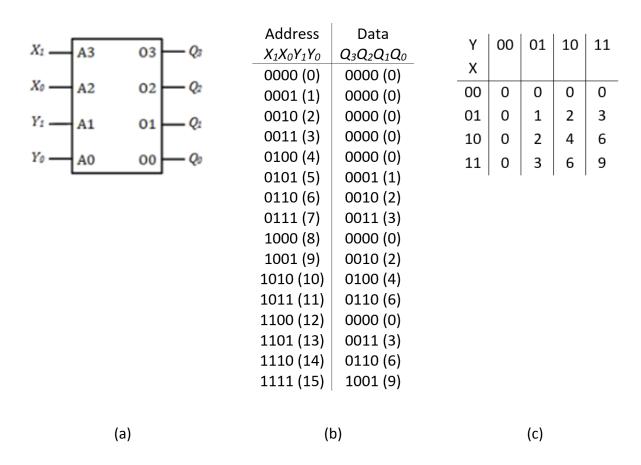

I have found that illustrating concepts using simple examples helps my students learn the material better. Some are absurdly simple. No company manufactures an 8x2 memory chip, but showing how such a chip functions gives students the base knowledge they need to design larger, more realistic memory chips.

#### **Scope of Coverage**

This book consists of ten chapters divided into four parts, as described below.

#### Part I: Background

This part, comprising the first two chapters, provides fundamental background information. The first chapter focuses on number systems, with an emphasis on binary numbers and different formats used to represent numbers. Several representations for nonnumeric data are also presented. This chapter also introduces Gray codes, special sequences of binary values that change only one bit at a time. Later, we use Gray codes to minimize functions and to design sequential circuits.

Chapter 2 introduces Boolean algebra, the mathematical basis for digital logic design. This chapter covers the fundamental Boolean functions and mechanisms used to represent function values, including truth tables, sum of products, product of sums, minterms, and maxterms. Minimizing functions is an essential design practice that reduces the hardware needed to implement the function. Two mechanisms used to minimize functions, Karnaugh maps and the Quine-McCluskey algorithm, are presented. This chapter concludes by examining how to develop and minimize functions when the function value is not specified for some combinations of input values.

#### **Part II: Combinatorial Logic**

Chapters 3, 4, and 5 focus on combinatorial logic, circuits that produce output values based solely on the current values of the inputs. Chapter 3 introduces the basic logic gates, digital components that implement the fundamental Boolean functions introduced earlier in this book. This chapter also presents methods to combine these gates to realize more complex functions and the inverse of these functions. Digital components are subject to real-world constraints that may not be reflected in the underlying Boolean algebra models. This chapter discusses fanin and fan-out, buffers, and propagation delay.

Some functions are used very frequently in digital design. Rather than recreate circuits for these functions every time they are used, engineers have created chips and components to implement these functions. When needed in a circuit, a digital design can simply plug the chip directly into a circuit. This chapter introduces the function and design of these components: decoders, encoders, multiplexers, demultiplexers, comparators, and adders. It also discusses tri-state buffers, a special type of buffer with numerous applications in digital logic design.

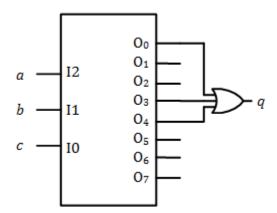

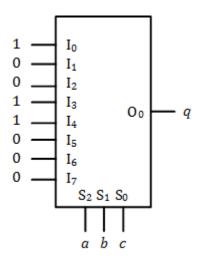

Chapter 5 uses some of these components to implement Boolean functions. It presents methodologies for realizing functions using multiplexers and decoders. This chapter also introduces ROMs, read-only memory components that can be used to realize functions by looking up function values. This chapter presents only the very basics of ROMs. They are covered in more detail later in this book.

#### **Part III: Sequential Logic**

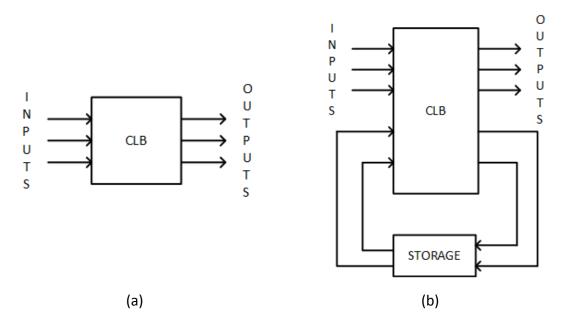

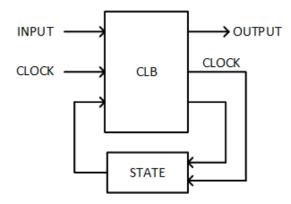

Unlike combinatorial logic, sequential logic generates outputs based on both its input values and its current state, or current internal conditions or values. Depending on its current state, the same input values may produce different output values and change to different next states.

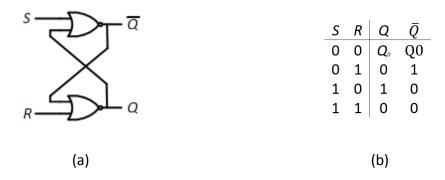

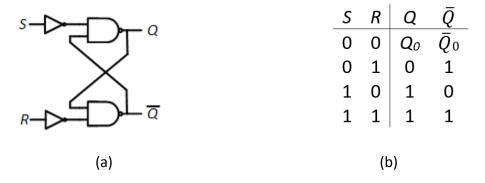

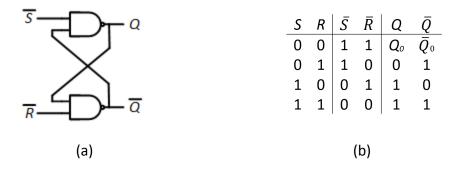

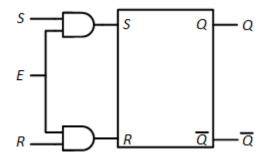

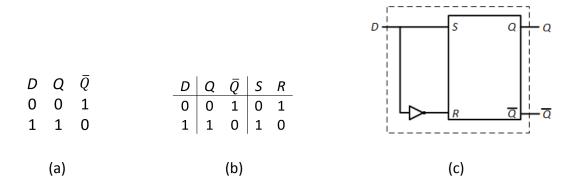

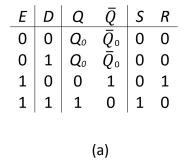

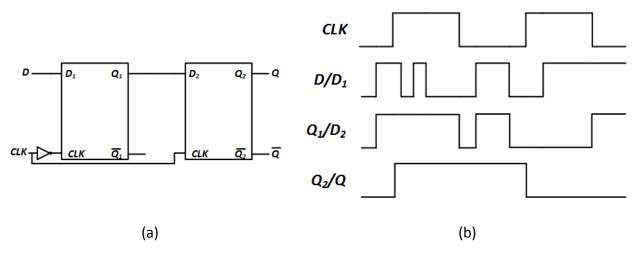

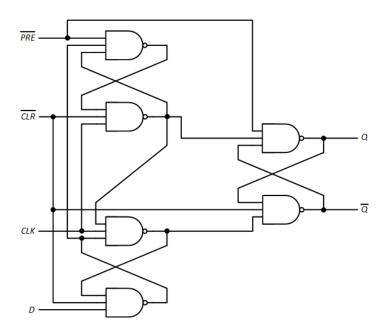

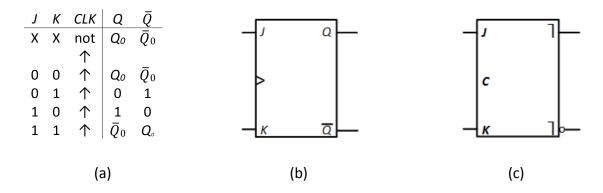

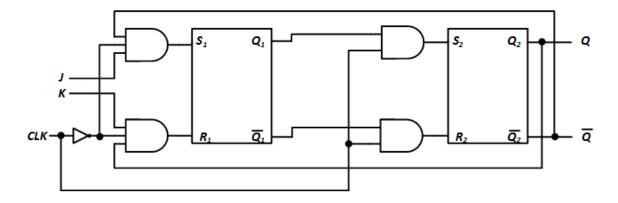

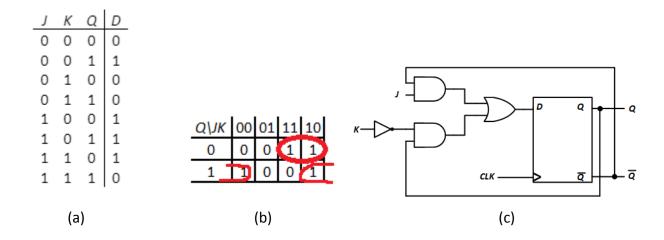

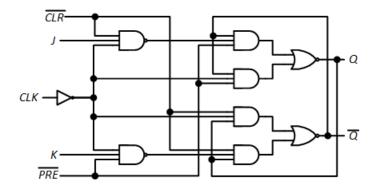

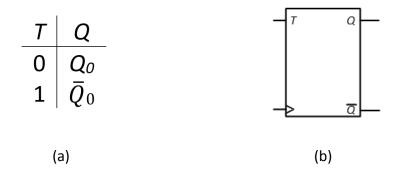

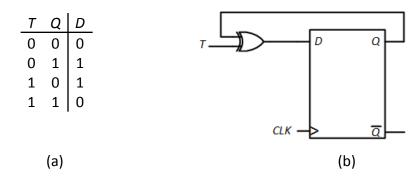

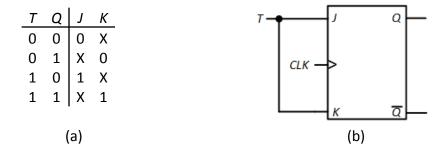

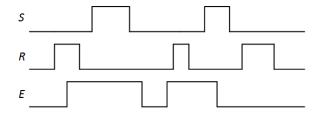

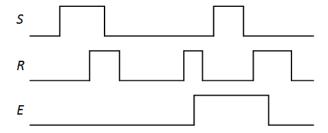

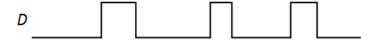

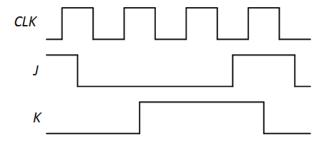

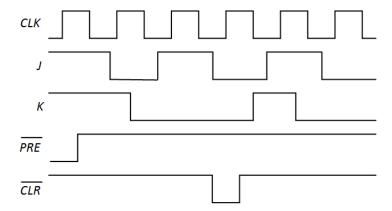

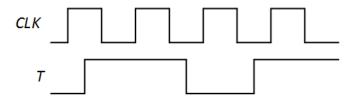

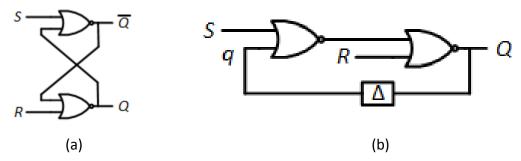

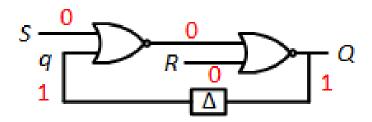

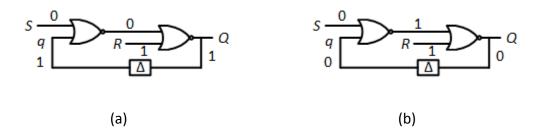

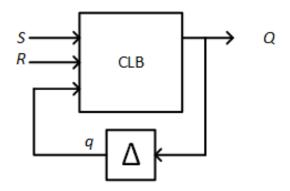

Chapter 6 introduces the basic model for sequential circuits and the fundamental components. Latches come in several varieties, including the S-R and D latches. This chapter introduces these components and their internal designs. Flip-flops, like latches, store binary values. Unlike latches, however, they load in values only on a clock edge, when the clock value changes from 0 to 1 or from 1 to 0. This chapter presents the internal designs and overall function of the D, J-K, and T flip-flops.

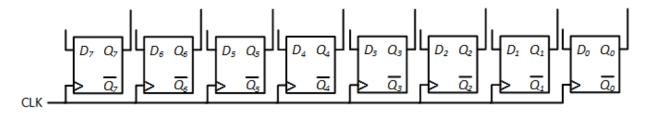

Just as engineers created more complex components for frequently used combinatorial functions, they have done the same for sequential components. This chapter introduces registers, which are used to store multi-bit values. Some registers can perform operations on their data. This chapter introduces several varieties of shift registers and counters and their internal designs.

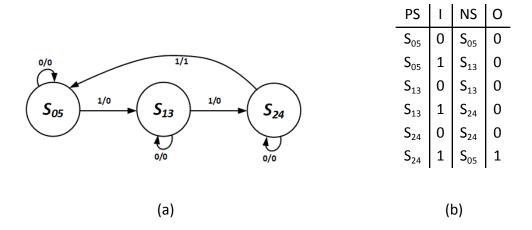

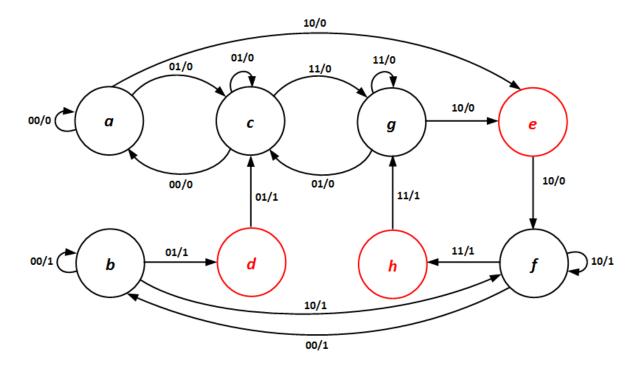

With this foundational knowledge in place, Chapter 8 focuses on the design of sequential circuits. There are two primary models for sequential circuits: Mealy and Moore machines. Both are introduced and used to design several sequential systems. This chapter also introduces tools used in the design of these systems, including state diagrams and state tables. The designs presented here use fundamental and more complex components; this chapter discusses the methodology used for each of these. It also examines how to refine and optimize designs when some values are not specified, how to identify and combine equivalent states, and how to deal with signal glitches.

#### **Part IV: Advanced Topics**

The final two chapters present two advanced topics. Chapter 9 presents asynchronous circuits. Unlike the sequential circuits introduced in the previous chapter, asynchronous circuits do not have a clock signal to coordinate the flow of data within the circuit. This impacts how we analyze and design these circuits. Asynchronous circuit designers must contend with several issues that are not found, or are found much less frequently, in sequential circuits. This chapter presents methods to identify and eliminate issues including unstable circuits, static and dynamic hazards, and race conditions.

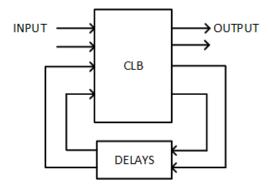

The final chapter examines programmable components. Programmable logic devices incorporate numerous logic gates and, for some PLDs, flip-flops. Designers specify the connections between components and between components and system inputs and outputs, to design a circuit within a single chip. This chapter also expands on the read-only memory (ROM) component briefly introduced in Chapter 5. It discusses the different types of memory devices and their internal designs.

## **Acknowledgments**

Although I am the sole author of this book, its creation, and development were influenced and implemented by a large number of people. The greatest influence has been my students. They have given me very useful feedback as to what works best when presenting material. This led me to incorporate animation throughout this book and has also moved me to change how I present material in my courses, for the better, I hope.

Most of this book was written during a sabbatical leave provided by my home university, the New Jersey Institute of Technology, through its Faculty Authored Open Textbook (FAOT) program, which is a part of NJIT's Open and Affordable Textbook Initiative. I am grateful to NJIT for providing this opportunity. I could not have completed this textbook in this timeframe, or possibly at all, without this support.

Through the Open and Affordable Textbook (OAT) Initiative's FAOT program, NJIT provided support for the production of the final version of this book, converting my text and graphics files into a final product. Thanks to Ann Hoang, University Librarian and coordinator of the OAT's FAOT program, and her staff who brought this book to fruition: Matthew Brown, Jennifer A. King, John Kromer, Jill Lagerstrom, Lisa Lakomy, Lisa Weissbard, Tim Valente, and Raymond Vasquez.

My colleagues at NJIT, both in the Helen and John C. Hartmann Department of Electrical and Computer Engineering and throughout the university, have had a great influence on this book, both its material and how it is presented. Special thanks to Professor Jacob Savir, course coordinator for our digital system design course. His advice, and especially his notes on asynchronous systems, were very helpful when preparing this material for this book.

I created most of the figures in this book using Microsoft Visio, with some figures using Word, Excel, and Paint for tables and minor tweaks. Thanks to Texas Instruments for granting permission to reproduce a couple of figures from their publications. I created the animations using the free converters at EZGIF.COM, with a little help from Adobe Photoshop for a couple of the more complex animations. Many thanks to the team at EZGIF for making this tool available to me and everyone.

Finally, last but certainly not least, I thank my family and friends for their love and support throughout the time writing this book, and really throughout my entire life. I especially thank my wife, Mary, my children, Maria and Tony, and my parents Dominick and Nina, to all of whom I dedicate this book.

## **Table of Contents**

#### **PART I: BACKGROUND**

| Ch | napter 1: Digital Systems and Numbers       | 1-2 |

|----|---------------------------------------------|-----|

|    | 1.1 What Are Digital Systems?               | 1-2 |

|    | 1.2 One and Zero                            | 1-3 |

|    | 1.3 Representing Numbers in Binary – Basics | 1-5 |

|    | 1.3.1 How Binary Numbers Work               | 1-5 |

|    | 1.3.2 Octal and Hexadecimal Notations       |     |

|    | 1.3.3 Converting from Decimal to Binary     |     |

|    | 1.4 Numeric Formats                         |     |

|    | 1.4.1 Unsigned Formats                      |     |

|    | 1.4.2 Signed Notations                      |     |

|    | 1.4.3 Floating Point Numbers                |     |

|    | 1.5 Representing Nonnumeric Data            |     |

|    | 1.5.1 ASCII                                 |     |

|    | 1.5.2 UNICODE                               |     |

|    | 1.6 Gray Code                               |     |

|    | 1.7 Summary                                 |     |

|    | Bibliography                                |     |

|    | Exercises                                   |     |

|    |                                             |     |

| Ch | napter 2: Boolean Algebra                   | 2-2 |

|    | 2.1 Boolean Algebra                         | 2-2 |

|    | 2.1.1 Boolean Algebra Fundamentals          | 2-3 |

|    | 2.1.2 Truth Tables                          | 2-3 |

|    | 2.1.3 Boolean Algebra Properties            | 2-4 |

|    | Closure                                     | 2-4 |

|    | Identity Elements                           | 2-5 |

|    | Commutativity                               |     |

|    | Distributivity                              | 2-6 |

|    | Inverse                                     |     |

|    | Distinct Elements                           | 2-7 |

|    | Idempotence                                 |     |

|    | ·                                           |     |

| Involution                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-8               |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|

| Absorption                                                                                                                                                                                                                                                                                                                                                                                                                   | 2-8               |

| Associativity                                                                                                                                                                                                                                                                                                                                                                                                                | 2-9               |

| De Morgan's Laws                                                                                                                                                                                                                                                                                                                                                                                                             | 2-10              |

| 2.2 Boolean Functions                                                                                                                                                                                                                                                                                                                                                                                                        | 2-11              |

| 2.2.1 Sum of Products                                                                                                                                                                                                                                                                                                                                                                                                        | 2-13              |

| 2.2.2 Product of Sums                                                                                                                                                                                                                                                                                                                                                                                                        | 2-14              |

| 2.2.3 The Relationship Between Minterms and Maxterms                                                                                                                                                                                                                                                                                                                                                                         | 2-15              |

| 2.2.4 Additional Examples                                                                                                                                                                                                                                                                                                                                                                                                    | 2-16              |

| 2.3 Minimizing Functions                                                                                                                                                                                                                                                                                                                                                                                                     | 2-18              |

| 2.3.1 Karnaugh Maps                                                                                                                                                                                                                                                                                                                                                                                                          | 2-18              |

| 2.3.1.1 2-Input Maps                                                                                                                                                                                                                                                                                                                                                                                                         | 2-19              |

| 2.3.1.2 3-Input Maps                                                                                                                                                                                                                                                                                                                                                                                                         | 2-21              |

| 2.3.1.3 4-Input Maps                                                                                                                                                                                                                                                                                                                                                                                                         | 2-24              |

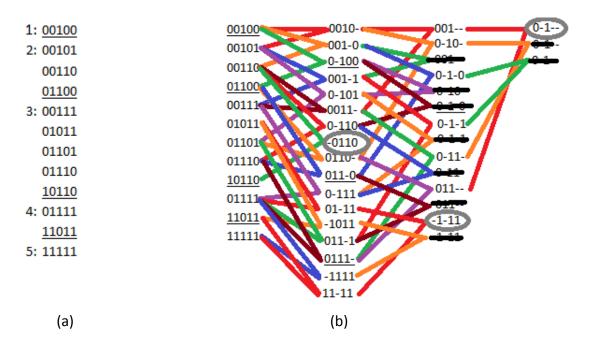

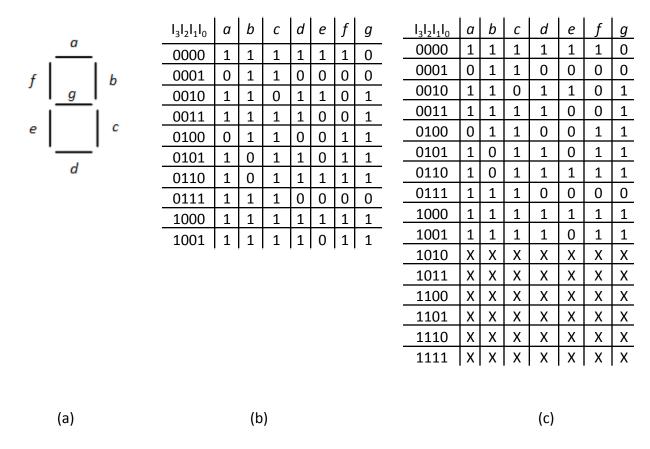

| 2.3.2 Quine-McCluskey Algorithm                                                                                                                                                                                                                                                                                                                                                                                              | 2-25              |

| 2.3.3 Don't Care Values and Incompletely Specified Functions                                                                                                                                                                                                                                                                                                                                                                 | 2-31              |

| 2.4 Summary                                                                                                                                                                                                                                                                                                                                                                                                                  | 2-34              |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                                                 | 2-35              |

|                                                                                                                                                                                                                                                                                                                                                                                                                              | 2.26              |

| Exercises                                                                                                                                                                                                                                                                                                                                                                                                                    | 2-36              |

| PART II: COMBINATORIAL LOGIC                                                                                                                                                                                                                                                                                                                                                                                                 | 2-36              |

|                                                                                                                                                                                                                                                                                                                                                                                                                              |                   |

| PART II: COMBINATORIAL LOGIC                                                                                                                                                                                                                                                                                                                                                                                                 | 3-2               |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals                                                                                                                                                                                                                                                                                                                                                          | <b>3-2</b>        |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates                                                                                                                                                                                                                                                                                                                                   | 3-2<br>3-2<br>3-5 |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions                                                                                                                                                                                                                                                                                                       | 3-23-23-53-5      |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic                                                                                                                                                                                                                                                                               |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals                                                                                                                                                                                                                                                                                                                                                          |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums                                                                                                                                                                       | 3-23-53-53-73-10  |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums  3.3 Inverse Functions                                                                                                                                                |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums  3.3 Inverse Functions  3.3.1 Inverse Functions Using Minterms                                                                                                        |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums  3.3 Inverse Functions  3.3.1 Inverse Functions Using Minterms  3.3.2 Inverse Functions Using Maxterms                                                                |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums  3.3 Inverse Functions  3.3.1 Inverse Functions Using Minterms  3.3.2 Inverse Functions Using Maxterms  3.3.3 What Inverse Functions Really Are                       |                   |

| PART II: COMBINATORIAL LOGIC  Chapter 3: Digital Logic Fundamentals  3.1 Basic Logic Gates  3.2 Implementing Functions  3.2.1 Minimizing Logic  3.2.2 Implementing Functions Using Sum of Products  3.2.3 Implementing Functions Using Product of Sums  3.3 Inverse Functions  3.3.1 Inverse Functions Using Minterms  3.3.2 Inverse Functions Using Maxterms  3.3.3 What Inverse Functions Really Are  3.4 Beyond the Logic |                   |

| 3.4.4 Propagation Delay            | 3-16          |

|------------------------------------|---------------|

| 3.5 Summary                        | 3-18          |

| Bibliography                       | 3-19          |

| Exercises                          | 3-20          |

| Chapter 4: More Complex Components | 4-2           |

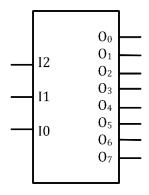

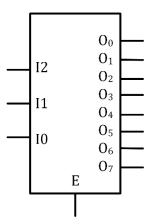

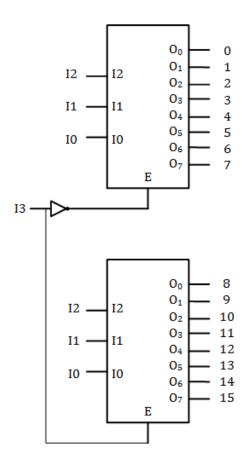

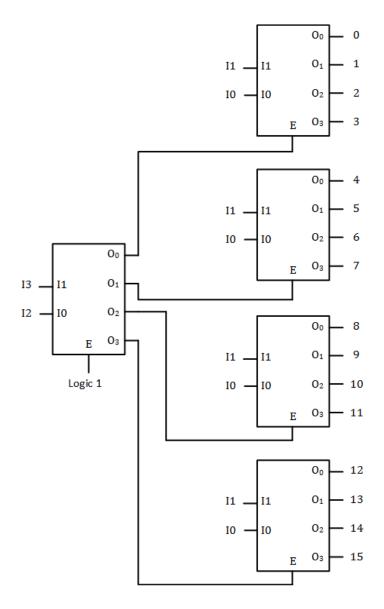

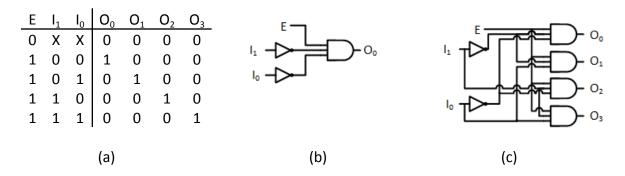

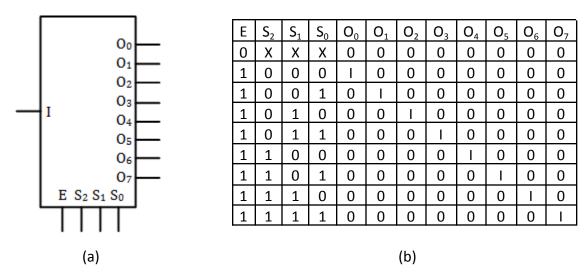

| 4.1 Decoders                       | 4-2           |

| 4.1.1 Decoder Basics               | 4-2           |

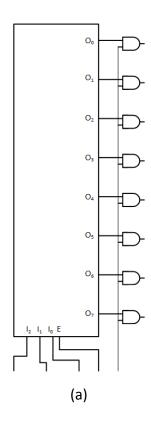

| 4.1.2 Decoder Internal Design      | 4-6           |

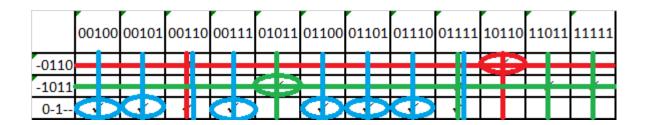

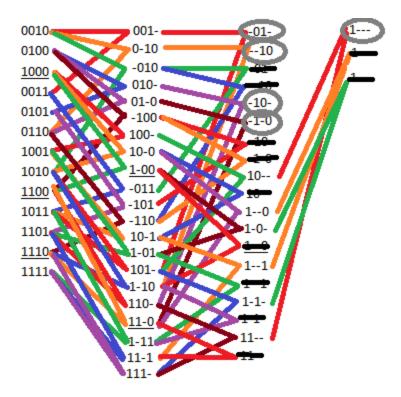

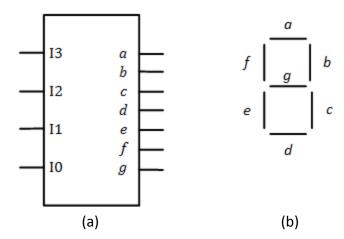

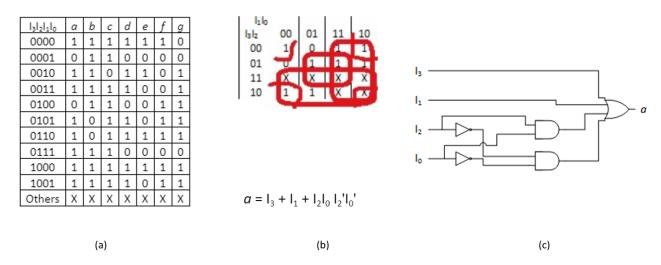

| 4.1.3 BCD to 7-segment Decoder     | 4-6           |

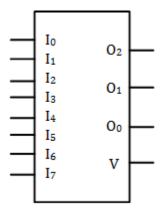

| 4.2 Encoders                       | 4-8           |

| 4.2.1 Encoder Basics               | 4-8           |

| 4.2.2 Encoder Internal Design      | 4-11          |

| 4.2.3 Priority Encoders            | 4-12          |

| 4.3 Multiplexers                   | 4-13          |

| 4.3.1 Multiplexer Basics           | 4-13          |

| 4.3.2 Multiplexer Internal Design  | 4-15          |

| 4.4 Demultiplexers                 | 4-17          |

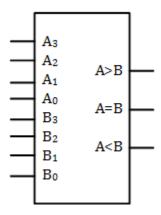

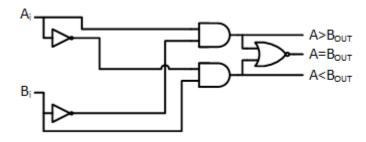

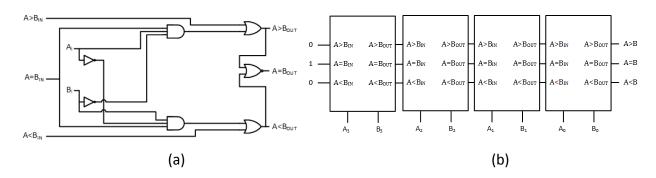

| 4.5 Comparators                    | 4-19          |

| 4.6 Adders                         | 4-22          |

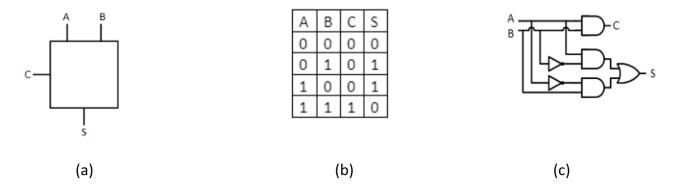

| 4.6.1 Half Adders                  | 4-22          |

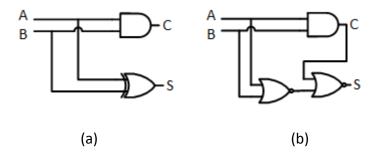

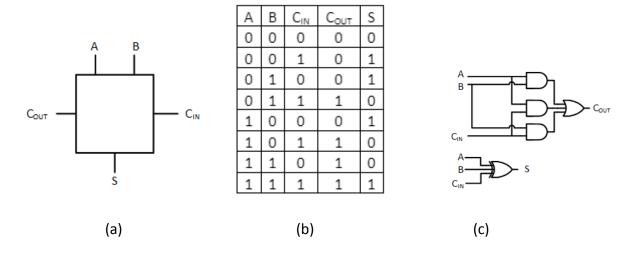

| 4.6.2 Full Adders                  | 4-23          |

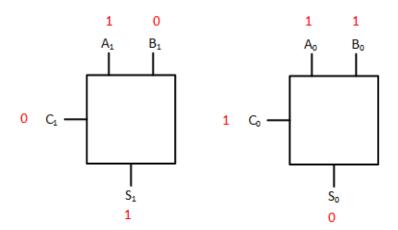

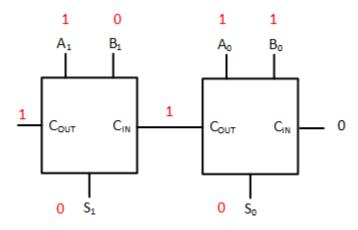

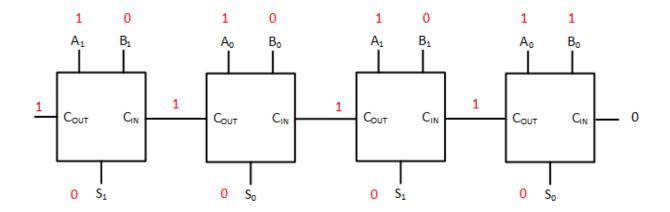

| 4.6.3 Ripple Adders                | 4-25          |

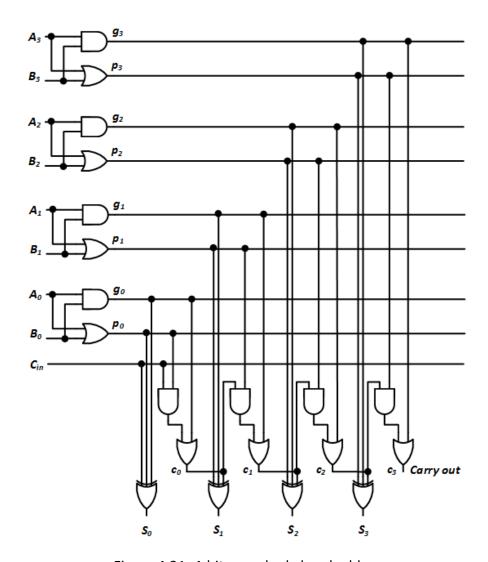

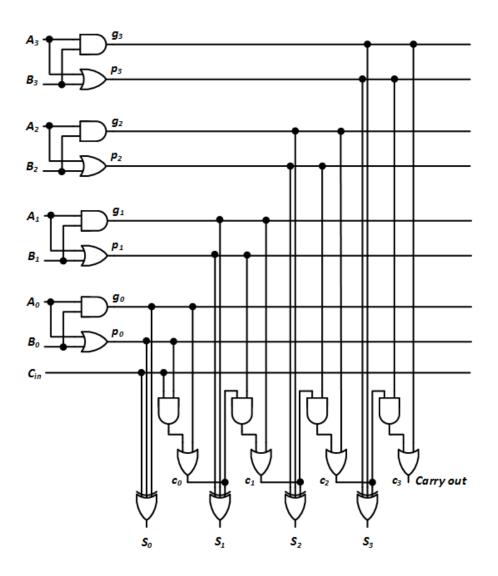

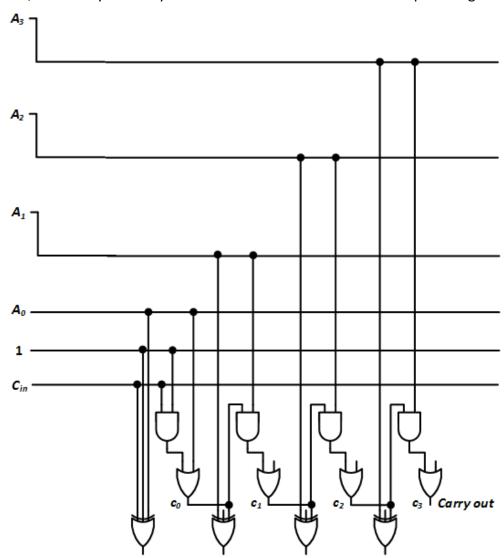

| 4.6.4 Carry-lookahead Adders       | 4-25          |

| 4.7 Tri-state Buffers              | 4-29          |

| 4.8 Summary                        | 4-31          |

| Bibliography                       | 4-32          |

| Exercises                          | 4-33          |

| Chapter 5: More Complex Functions  | 5-2           |

| ·                                  | oders5-2      |

|                                    | ziplexers 5-4 |

|                                    | 5-8           |

|                                    | 5-8           |

| ·                                  | 5-9           |

|                                    | s5-10         |

|                                    | its 5-12      |

|                                    |               |

| 5.4 Summary                                      | 5-14 |

|--------------------------------------------------|------|

| Bibliography                                     | 5-15 |

| Exercises                                        | 5-16 |

|                                                  |      |

| PART III: SEQUENTIAL LOGIC                       |      |

| Chapter 6: Sequential Components                 | 6-2  |

| 6.1 Modeling Sequential Circuits                 |      |

| 6.1.1 What Is a State?                           |      |

| 6.1.2 What Is a Clock?                           |      |

| 6.1.3 Asynchronous Sequential Circuits           |      |

| 6.2 Latches                                      |      |

| 6.2.1 S-R Latch                                  |      |

| 6.2.2 S-R Latch with Enable                      |      |

| 6.2.3 D Latch                                    |      |

| 6.3 Flip-Flops                                   |      |

| 6.3.1 D Flip-Flop                                |      |

| 6.3.1.1 Leader-Follower Design                   |      |

| 6.3.1.2 Preset and Clear                         |      |

| 6.3.2 J-K Flip-Flop                              |      |

| 6.3.3 T Flip-Flop                                |      |

| 6.4 Summary                                      |      |

| Bibliography                                     |      |

| Exercises                                        |      |

| Chautau 7, Mara Camulau Camuantial Camunananta   | 7.3  |

| Chapter 7: More Complex Sequential Components    |      |

| 7.1 Registers                                    |      |

| 7.2 Shift Registers                              |      |

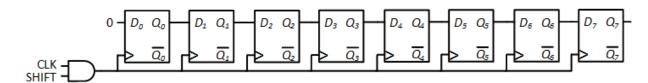

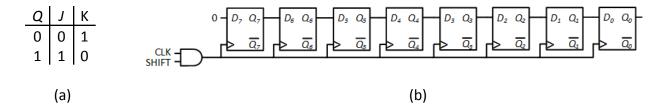

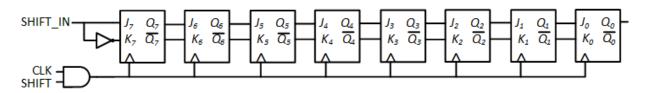

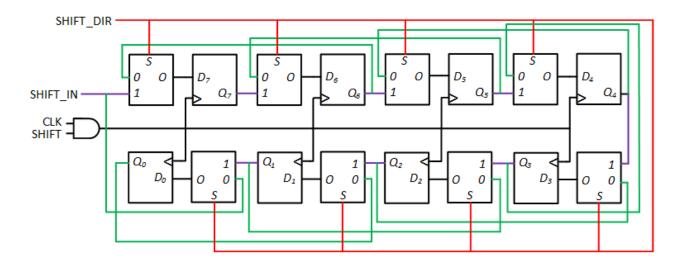

| 7.2.1 Linear Shifts                              |      |

| 7.2.2 Shift Register Design Using D Flip-Flops   |      |

| 7.2.3 Shift Register Design Using J-K Flip-Flops |      |

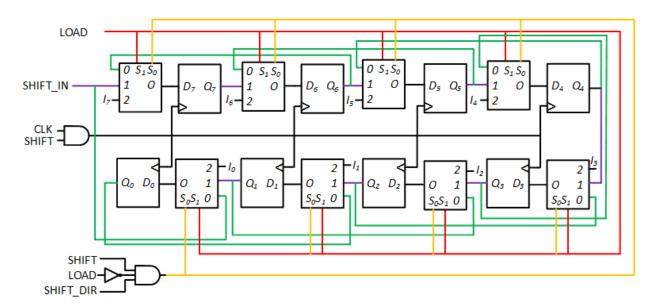

| 7.2.4 Bidirectional Shift Registers              |      |

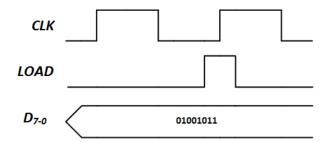

| 7.2.5 Shift Registers with Parallel Load         |      |

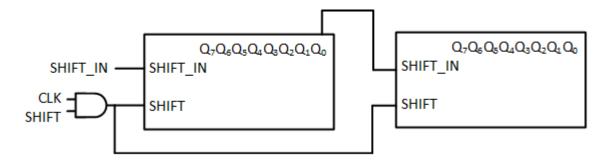

| 7.2.6 Combining Shift Registers                  |      |

| 7.3 Counters                                     |      |

| 7.4 Binary Counters – Function                   | 7-12 |

|    | 7.5 Binary Counters – Design                                           | 7-13 |

|----|------------------------------------------------------------------------|------|

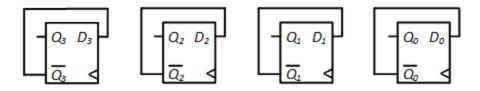

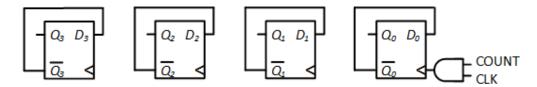

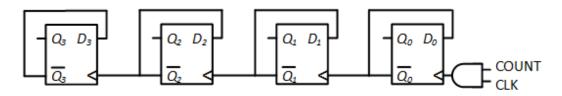

|    | 7.5.1 Ripple Counters                                                  | 7-13 |

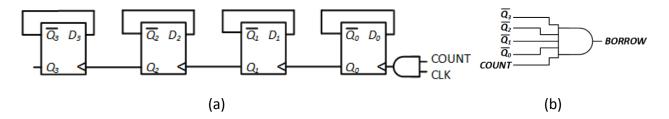

|    | 7.5.1.1 Downcounter                                                    | 7-16 |

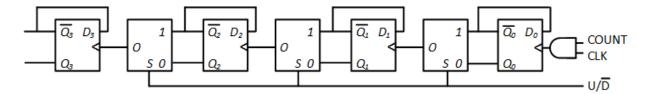

|    | 7.5.1.2 Up/Down Counter                                                | 7-16 |

|    | 7.5.1.3 Additional Signals                                             | 7-17 |

|    | 7.5.1.4 Why Are They Called Ripple Counters?                           | 7-17 |

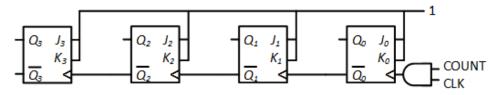

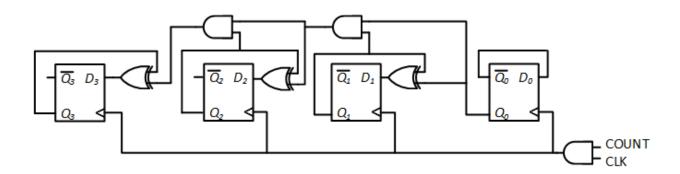

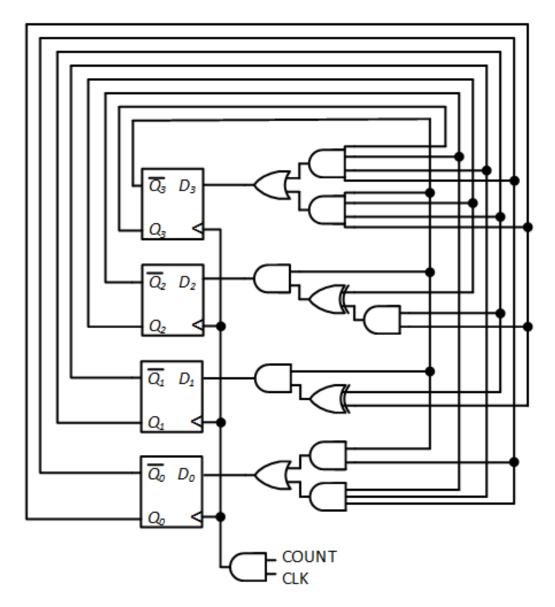

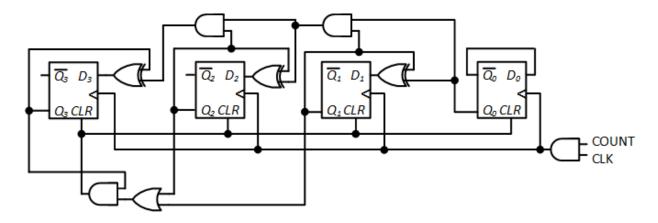

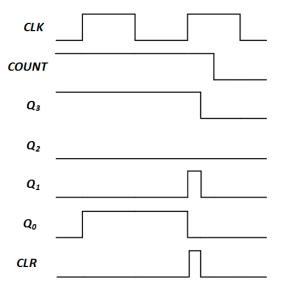

|    | 7.5.2 Synchronous Counters                                             | 7-18 |

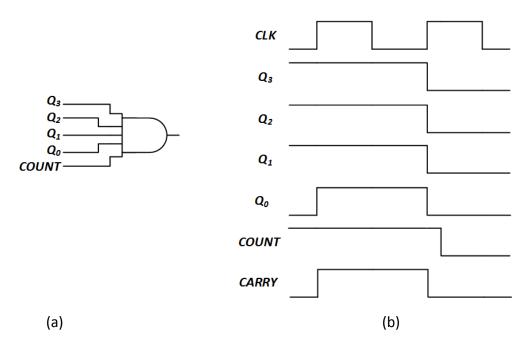

|    | 7.6 Cascading Counters                                                 | 7-25 |

|    | 7.7 Other Counters                                                     | 7-25 |

|    | 7.7.1 BCD Counters                                                     | 7-25 |

|    | 7.7.2 Modulo-n Counters                                                | 7-27 |

|    | 7.8 Summary                                                            | 7-29 |

|    | Bibliography                                                           | 7-31 |

|    | Exercises                                                              | 7-32 |

| Cł | apter 8: Sequential Circuits                                           | 8-2  |

|    | 8.1 Finite State Machines – Basics                                     | 8-2  |

|    | 8.1.1 What Is a State?                                                 | 8-2  |

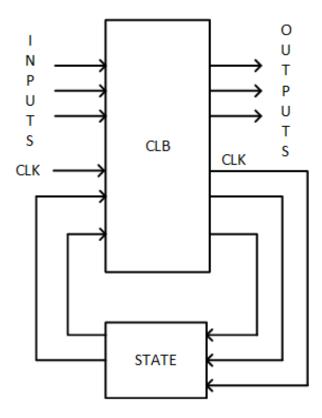

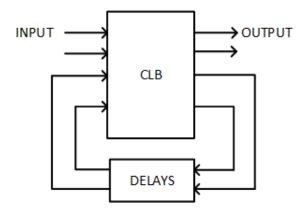

|    | 8.1.2 System Model                                                     | 8-3  |

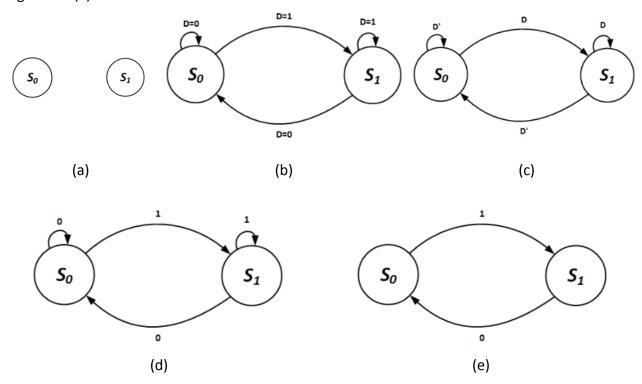

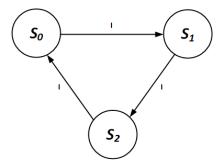

|    | 8.1.3 State Diagrams (Excluding Outputs)                               | 8-4  |

|    | 8.1.4 State Tables (Also Excluding Outputs)                            | 8-6  |

|    | 8.2 Types of Finite State Machines                                     | 8-7  |

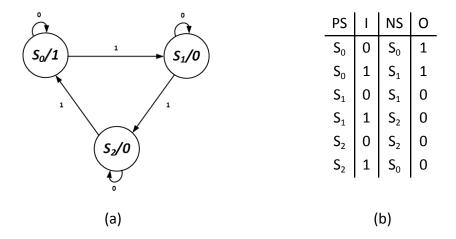

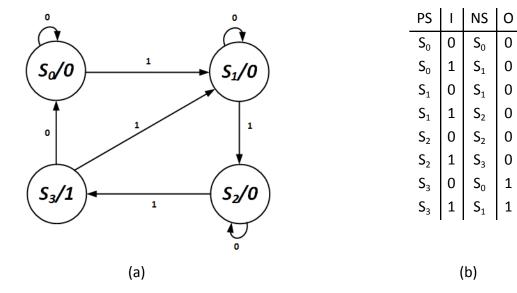

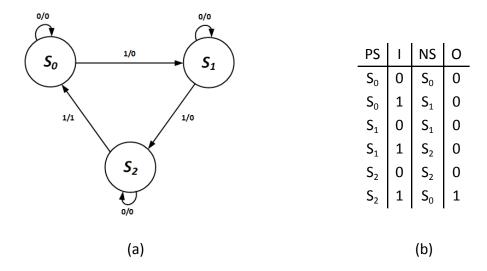

|    | 8.2.1 Mealy Machines                                                   | 8-7  |

|    | 8.2.2 Moore Machines                                                   | 8-10 |

|    | 8.2.3 A Word About Infinite State Machines                             | 8-12 |

|    | 8.3 Design Process                                                     | 8-12 |

|    | Step 1: Specify System Behavior                                        | 8-13 |

|    | Step 2: Determine States and Transitions, and Create the State Diagram | 8-13 |

|    | Step 3: Create State Table with State Labels                           | 8-13 |

|    | Step 4: Assign Binary Values to States                                 | 8-14 |

|    | Step 5: Update the State Table with the Binary State Values            | 8-14 |

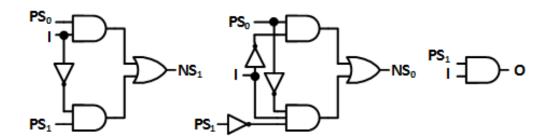

|    | Step 6: Determine Functions for the Next State Bits and Outputs        | 8-14 |

|    | Step 7: Implement the Functions Using Combinatorial Logic              | 8-14 |

|    | 8.3.1 Design Example – Mealy Machine                                   | 8-15 |

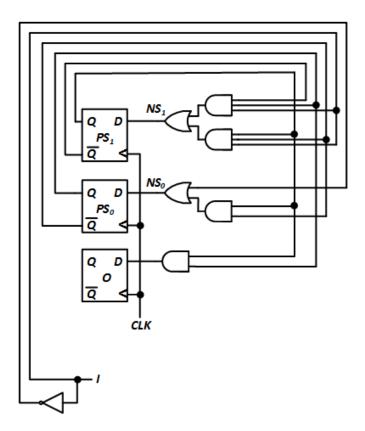

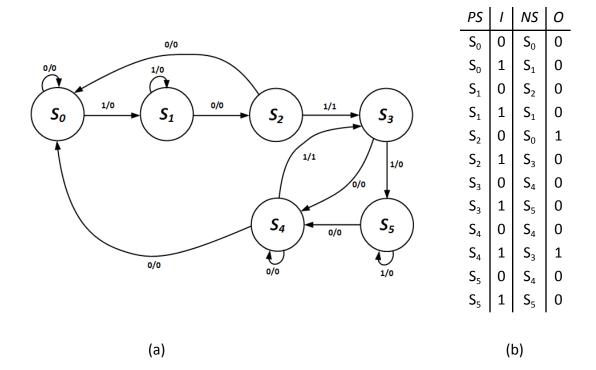

|    | 8.3.2 Design Example – Moore Machine                                   | 8-17 |

|    | 8.3.3 A Brief Word About Flip-Flops                                    | 8-19 |

|    | 8.3.4 Comparing our Two Designs                                        | 8-20 |

| 8.4 Design Using More Complex Components                                                                                                                                                                                                                                                                                                                                                                 | 8-20                                |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| 8.4.1 Design Using a Counter                                                                                                                                                                                                                                                                                                                                                                             | 8-20                                |

| Step 1: Specify System Behavior                                                                                                                                                                                                                                                                                                                                                                          | 8-21                                |

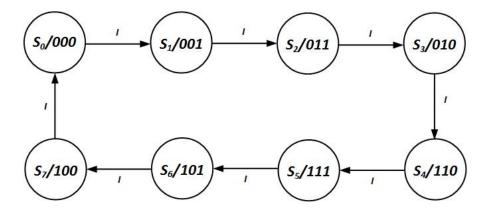

| Step 2: Determine States and Transitions, and Create the State Diagra                                                                                                                                                                                                                                                                                                                                    | m 8-21                              |

| Step 3: Create State Table with State Labels                                                                                                                                                                                                                                                                                                                                                             | 8-21                                |

| Step 4: Assign Binary Values to States                                                                                                                                                                                                                                                                                                                                                                   | 8-22                                |

| Step 5: Update the State Table with the Binary State Values                                                                                                                                                                                                                                                                                                                                              | 8-22                                |

| Step 6: Determine Functions for the Next State Bits and Outputs                                                                                                                                                                                                                                                                                                                                          | 8-23                                |

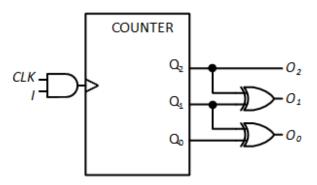

| Step 7: Implement the Functions Using Combinatorial Logic                                                                                                                                                                                                                                                                                                                                                | 8-24                                |

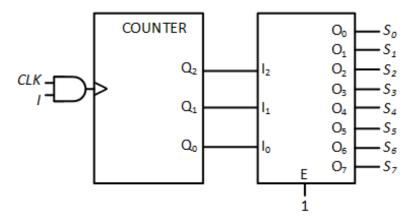

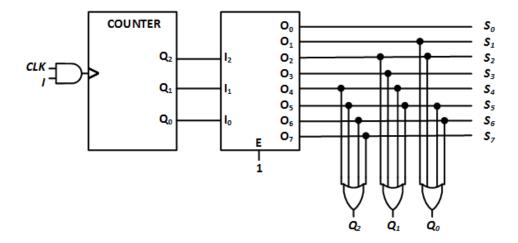

| 8.4.2 Design Using a Decoder                                                                                                                                                                                                                                                                                                                                                                             | 8-25                                |

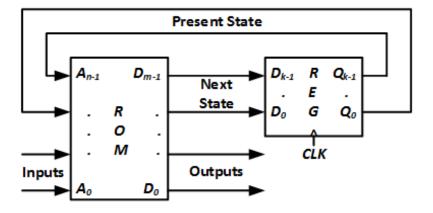

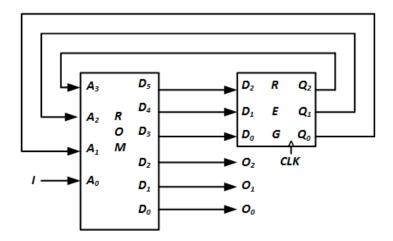

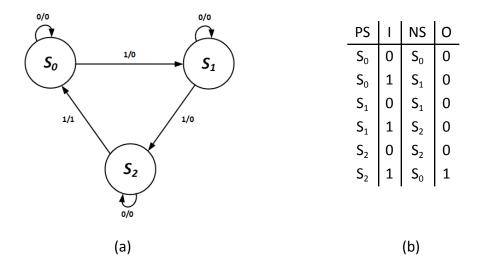

| 8.4.3 Design Using a Lookup ROM                                                                                                                                                                                                                                                                                                                                                                          | 8-27                                |

| 8.5 Refining Your Designs                                                                                                                                                                                                                                                                                                                                                                                | 8-30                                |

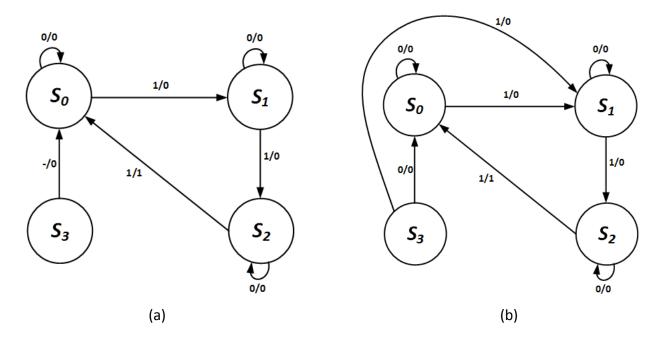

| 8.5.1 Unused States                                                                                                                                                                                                                                                                                                                                                                                      | 8-30                                |

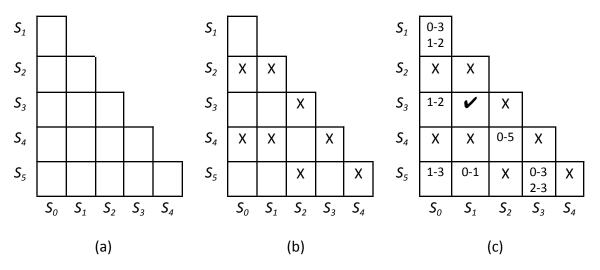

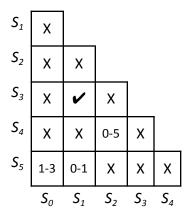

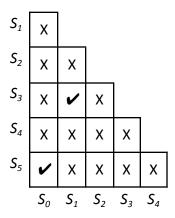

| 8.5.2 Equivalent States                                                                                                                                                                                                                                                                                                                                                                                  | 8-33                                |

| 8.5.3 Glitches                                                                                                                                                                                                                                                                                                                                                                                           | 8-38                                |

| 8.6 Summary                                                                                                                                                                                                                                                                                                                                                                                              | 8-40                                |

|                                                                                                                                                                                                                                                                                                                                                                                                          | 8-42                                |

| Bibliography                                                                                                                                                                                                                                                                                                                                                                                             | 8-43                                |

| Exercises                                                                                                                                                                                                                                                                                                                                                                                                |                                     |

| PART IV: ADVANCED TOPICS                                                                                                                                                                                                                                                                                                                                                                                 |                                     |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits                                                                                                                                                                                                                                                                                                                                    |                                     |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model                                                                                                                                                                                                                                                                                                            | 9-2                                 |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process                                                                                                                                                                                                                                                                                        | 9-2<br>9-3                          |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model                                                                                                                                                                                                                                                                                                            | 9-2<br>9-3                          |

| Exercises                                                                                                                                                                                                                                                                                                                                                                                                |                                     |

| Exercises  PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits                                                                                                                                                                                                                                                                                                                         |                                     |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process  9.2.1 Analysis Example  9.2.2 Design Example  Step 1: Develop System Specifications  Step 2: Define States                                                                                                                                                                            | 9-2<br>9-3<br>9-7<br>9-7            |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model                                                                                                                                                                                                                                                                                                            |                                     |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process  9.2.1 Analysis Example  9.2.2 Design Example  Step 1: Develop System Specifications  Step 2: Define States  Step 3: Minimize States  Step 4: Assign Binary Values to States                                                                                                           | 9-29-39-79-89-89-11                 |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model                                                                                                                                                                                                                                                                                                            | 9-29-39-79-79-89-119-11             |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model                                                                                                                                                                                                                                                                                                            | 9-29-39-79-79-89-119-13             |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process  9.2.1 Analysis Example  9.2.2 Design Example  Step 1: Develop System Specifications  Step 2: Define States  Step 3: Minimize States  Step 4: Assign Binary Values to States  Step 5: Determine Functions and Create Circuit  9.3 Unstable Circuits  9.4 Hazards                       | 9-29-39-79-79-89-119-119-139-15     |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process  9.2.1 Analysis Example  9.2.2 Design Example  Step 1: Develop System Specifications  Step 2: Define States  Step 3: Minimize States  Step 4: Assign Binary Values to States  Step 5: Determine Functions and Create Circuit  9.3 Unstable Circuits  9.4 Hazards  9.4.1 Static Hazards | 9-29-39-79-79-79-89-119-119-159-15  |

| PART IV: ADVANCED TOPICS  Chapter 9: Asynchronous Sequential Circuits  9.1 Overview and Model  9.2 Design Process  9.2.1 Analysis Example  9.2.2 Design Example  Step 1: Develop System Specifications  Step 2: Define States  Step 3: Minimize States  Step 4: Assign Binary Values to States  Step 5: Determine Functions and Create Circuit  9.3 Unstable Circuits  9.4 Hazards                       | 9-29-39-79-79-89-119-119-139-159-15 |

|    | 9.4.1.3 Recognizing and Resolving Static-O Hazards     | 9-18  |

|----|--------------------------------------------------------|-------|

|    | 9.4.2 Dynamic Hazards                                  | 9-20  |

|    | 9.5 Race Conditions                                    | 9-22  |

|    | 9.5.1 Non-critical Race Conditions                     | 9-22  |

|    | 9.5.2 Critical Race Conditions                         | 9-23  |

|    | 9.5.3 Resolving Critical Race Conditions               | 9-24  |

|    | 9.5.3.1 Another Example                                | 9-25  |

|    | 9.5.3.2 How Did We Do That?                            | 9-27  |

|    | 9.6 Summary                                            | 9-30  |

|    | Acknowledgment                                         | 9-31  |

|    | Bibliography                                           | 9-32  |

|    | Exercises                                              | 9-33  |

|    |                                                        |       |

| Ch | napter 10: Programmable Devices                        | 10-2  |

|    | 10.1 Why Programmable Devices?                         |       |

|    | 10.2 Programmable Logic Devices                        | 10-3  |

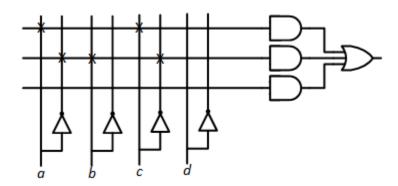

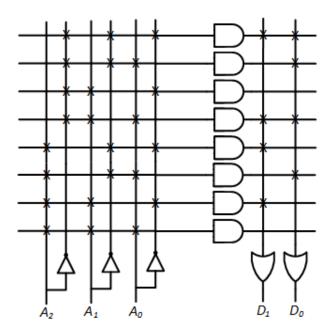

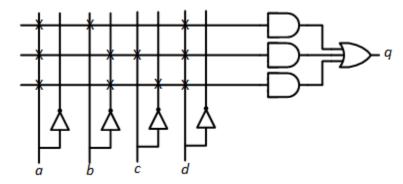

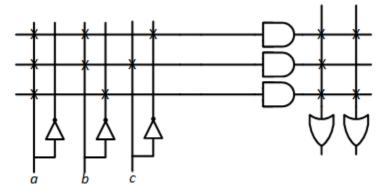

|    | 10.2.1 Programmable Array Logic                        |       |

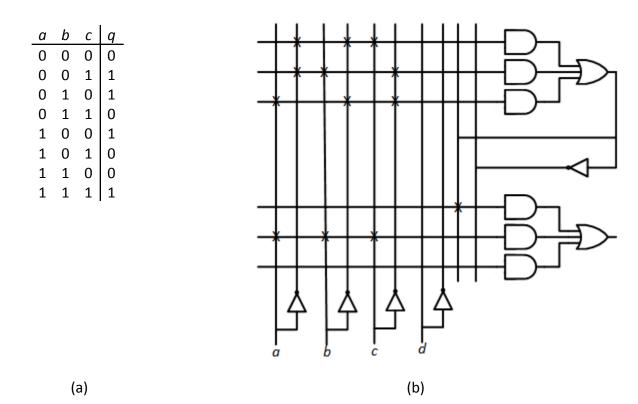

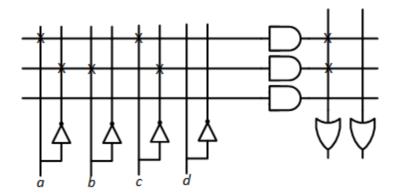

|    | 10.2.2 Programmable Logic Arrays                       | 10-5  |

|    | 10.2.3 Complex PLDs and Field Programmable Gate Arrays |       |

|    | 10.3 Memory Devices                                    | 10-7  |

|    | 10.3.1 Volatile Memory Devices                         | 10-7  |

|    | 10.3.2 Non-volatile Memory Devices                     | 10-8  |

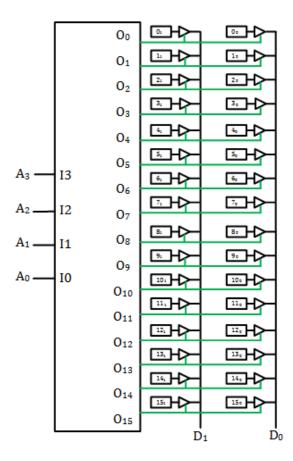

|    | 10.3.2.1 Masked ROM, or ROM                            | 10-9  |

|    | 10.3.2.2 Programmable ROM                              | 10-9  |

|    | 10.3.2.3 Erasable PROM                                 | 10-9  |

|    | 10.3.2.4 Electrically Erasable PROM                    | 10-10 |

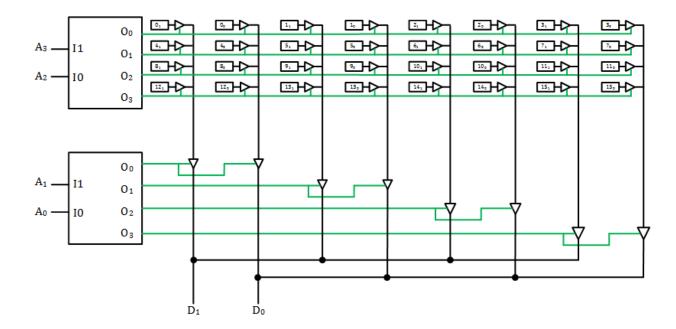

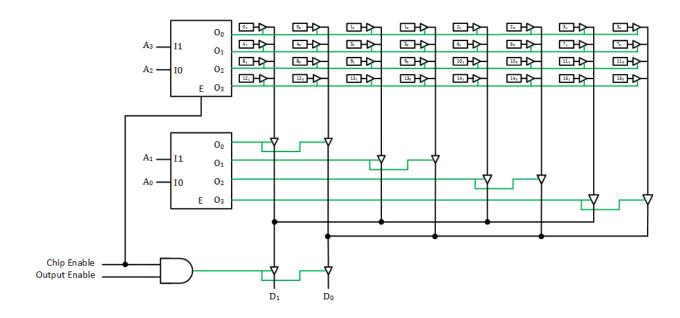

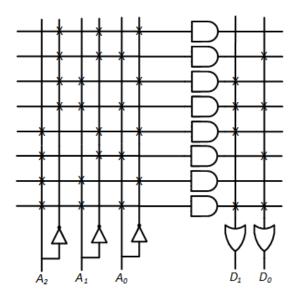

|    | 10.3.3 Internal Organization                           | 10-10 |

|    | 10.4 Summary                                           | 10-15 |

|    | Bibliography                                           | 10-17 |

|    | Eversises                                              | 1∩_1∘ |

# **PARTI**

# Introduction and Background

# Chapter 1

## Digital Systems and Numbers

Creative Commons License

Attribution-NonCommercial-ShareAlike 4.0 International (CC-BY-NC-SA 4.0)

#### Chapter 1: Digital Systems and Numbers

Digital systems are everywhere. From consumer appliances to the most advanced supercomputer, including the phone/tablet/computer you're using right now to read this e-book, virtually no aspect of our lives is untouched by these systems. To design these systems, the designer needs to understand what digital systems are (and are not), the mathematical background underlying digital systems, the components used in these systems, and how the digital design process works. We'll look at all of these as we progress through the book. In this chapter, we'll start with the basics.

Digital systems use **binary** values. Mathematically, binary is a base-2 system, where each value within the system is either 0 or 1. We'll look at what this means and how we represent these values in various media.

Just as we represent decimal numbers using more than one digit, we can represent binary numbers using more than one binary digit, or **bit**. In this chapter, we'll introduce several numeric formats used in some digital systems.

Binary values can also be used to represent nonnumeric data, such as alphanumeric characters (letters, numbers, and symbols). We'll look at a couple of the most commonly used formats.

Finally, this chapter introduces **Gray code**, a reflected binary code. We will make use of this code in Chapter 2 as we optimize our first digital designs.

#### 1.1 What Are Digital Systems?

The world is digital! Everything is run by computers! Digital this! Digital that! Blah, blah, blah. You've probably heard all of this and more. But what is digital? What does it mean to be digital? What is something if it isn't digital? And how do you design something that is digital?

These are all fair questions. The first three are pretty straightforward, and we'll discuss them shortly. However, exploring that last question could fill many textbooks.. This book will cover the basics of digital logic design for relatively simple systems. More advanced systems, such as computer systems and microprocessor design, build on the design methodologies presented here, but they are much more complex than those included in this book.

To answer the first question, let's start with a quote.

There may be said to be two kinds of people in the world, those who constantly divide everybody into two classes, and those who do not. – Robert Benchley

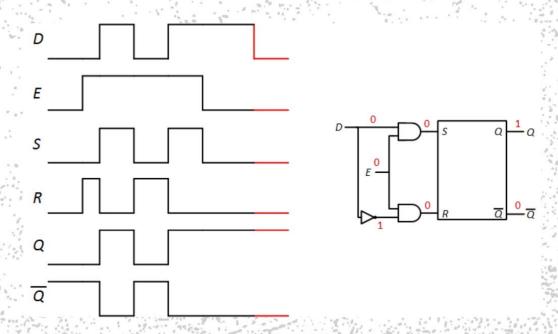

In this section, we're going to be the kind of people who divide electrical signals into two classes. **Analog** signals are continuous. They can take on any value within a given range. In the sine wave shown in Figure 1.1 (a), the amplitude (height) of the sine wave can take on any value from -1 to +1. Any value in this range corresponds to the amplitude at some point(s) on the sine wave.

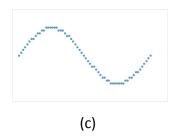

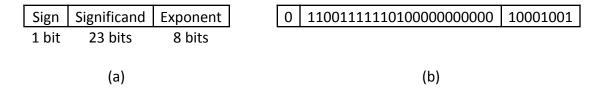

Figure 1.1: (a) Analog sine wave; (b) Digital representation with nine possible values; (c) Digital representation with nineteen possible values

In contrast, digital signals are **quantized**. They can only take on specific values, and there are gaps between these values. The digital signals can only approximate the equivalent analog values. Consider a digital system that can represent only these nine values: -1, -¾, -½, -¼, 0, ¼, ½, ¾, and 1. Figure 1.1 (b) shows how we could represent the sine wave in this digital system by rounding the value of the amplitude to its nearest digital value.

The digital wave is rather choppy as compared to the analog wave. However, we can make the digital wave more like the analog wave by increasing the number of possible values. The digital wave in Figure 1.1 (c) uses a digital system with 19 possible values: -1, -0.9, -0.8, -0.7, -0.6, -0.5, -0.4, -0.3, -0.2, -0.1, 0, 0.1, 0.2, 0.3, 0.4, 0.5, 0.6, 0.7, 0.8, 0.9, and 1. You can see this wave is not as smooth as the analog wave, but it is much smoother than the previous digital wave.

So, if analog gives us smoother curves and more accurate values, why should we even use digital? There are many reasons to use digital. Digital signals are less susceptible to noise during transmission, resulting in less distortion and better signal quality. Furthermore, transmission across greater distances is possible with digital than with analog. Digital signals can transmit more information (per second) than analog signals. Digital circuits are often cheaper to design and manufacture than analog circuits. There are other reasons as well.

#### 1.2 One and Zero

There are 10 kinds of people in the world, those who know binary, and those who don't. – Anonymous (with apologies to Robert Benchley)

When we examine digital logic, we see that it uses discrete values. Unlike decimal, which has ten digits, digital logic uses **binary** values. Binary is base 2, as opposed to base 10 for decimal, and it has only two digits. These are typically represented as 1 and 0. Each value is called a **bit**, short for binary digit. You can also think of these values as true and false (which can be helpful when we discuss Boolean algebra in Chapter 2), on and off (like a light switch, but only a regular toggle switch, not a dimmer switch), or yes and no. As we design digital circuits, we'll mostly use 1 and 0.

So, why do we use binary? Why not use ternary (base 3) or some other base? As it turns out, it is much simpler to design electronics that generate two possible values than it is to design circuits that can output three or more possible values. If we need more possible values,

we can combine more outputs to represent these values. We'll look at how to do this for numeric values in the next section.

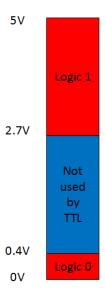

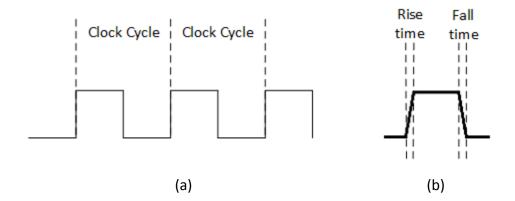

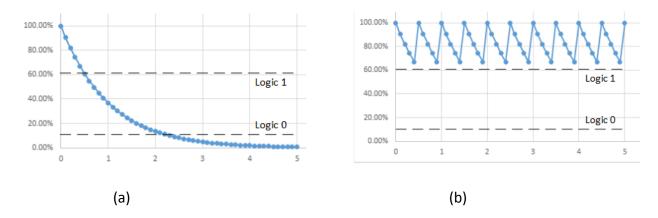

Now back to the electronics. Digital logic gates, the fundamental building blocks of digital systems, are constructed from transistors. Without going too in-depth, a transistor can be used in a circuit that is configured as a switch. When the switch is off, the circuit generates a very low voltage that corresponds to a logic value of 0. When it is on, it outputs a voltage that is interpreted as a logic value of 1. The circuit does not spend any appreciable time in the region between these two extremes, though it does spend some minimal time there as it transitions from one extreme to the other. Figure 1.2 shows these regions for transistor-transistor logic.

Figure 1.2: Voltage levels for transistor-transistor logic with a 5V source.

There are numerous ways to represent 1 and 0. As we just saw, voltage values are one way to do this. For TTL, transistor-transistor logic, 2.7V to 5V typically represents the logic value 1 and 0V to 0.4V represents logic 0. Values for other technologies are shown in Figure 1.3. Note that one technology, emitter-coupled logic, uses a negative power supply and thus has negative voltage values for its logic levels.

| Technology                                    | Source voltage | Logic 1   | Logic 0 |

|-----------------------------------------------|----------------|-----------|---------|

| TTL: transistor-transistor logic              | 5V             | 2.7-5V    | 0-0.4V  |

| CMOS: complementary metal-oxide semiconductor | 5V             | 4.44-5V   | 0-0.5V  |

|                                               | 3.3V           | 2.4-3.3V  | 0-0.4V  |

| ECL: Emitter-coupled logic                    | -5.2V          | -0.9V     | -1.75V  |

| PECL: Positive ECL                            | 5V             | 4.1V      | 0-3.3V  |

|                                               | 3.3V           | 2.27-3.3V | 0-1.68V |

Figure 1.3: Voltages corresponding to logic values for several technologies

Memory chips are used to store digital logic values. For the E<sup>2</sup>PROM memory chips used in flash drives, SD cards, and solid-state drives, these values are similar to those of TTL chips.

Voltage is not the only way to store digital logic values, though any other method ultimately must be converted to voltages to be used by the rest of a digital system. A traditional (non-SSD) drive stores each bit by magnetizing a portion of the disc in one of two directions. The drive has two heads to read values from the disc. Reading the value induces a current from one head to the other. The current flows in one of two directions, from the first head to the second or vice versa, depending on the magnetization of the disc at that point. Circuitry (connected to the heads of the disc drive) outputs a voltage value corresponding to logic 1 or logic 0 that depends on the direction of current flow.

Optical discs, including CDs, DVDs, and Blu-Ray, encode logic values in one of two ways. For pre-recorded discs, such as a movie you might buy on Blu-Ray (if anyone is still buying discs by the time you read this), the discs are manufactured with areas called **pits** and **lands** that reflect light. The disc drive shines a laser onto a portion of a disc that stores one bit and senses the intensity of the reflected light. A higher intensity corresponds to a logic value of 1 and a lower intensity denotes logic 0. Recordable optical discs, such as DVD RW, write data to the disc by darkening and lightening areas of the disc to achieve the same result. As an aside, note that Blu-Ray discs use lasers of a different frequency than CDs and DVDs which allows them to focus on a smaller area of the disc; this is why they can store more data than the other optical discs.

#### 1.3 Representing Numbers in Binary – Basics

Ultimately, we want to use binary values to represent all types of information. Foremost among these are numbers and alphanumeric characters. In this section, we'll introduce the basics of binary numbers. In the following sections we'll look at more complex numeric formats and formats for characters.

#### 1.3.1 How Binary Numbers Work

To explain how binary numbers work, first let's look at how decimal numbers work, since the general method is similar. The decimal number system has ten digits, 0 to 9, but it wouldn't be very useful if it could not represent values greater than nine. To do this, we use multiple digits in a number. The value of each digit is based on both its value as a digit and its place in the number. Consider, for example, the number 135.79. The 1 is in the hundreds place, so its value is  $1 \times 100 = 100$ . Similarly, the 3 has a value of  $3 \times 10 = 30$  because it is in the tens place, and so on for the remaining digits. We could expand this as

$$135.79 = (1 \times 100) + (3 \times 10) + (5 \times 1) + (7 \times 0.1) + (9 \times 0.01)$$

$$= (1 \times 10^{2}) + (3 \times 10^{1}) + (5 \times 10^{0}) + (7 \times 10^{-1}) + (9 \times 10^{-2})$$

Binary numbers are created in the same way, except we use powers of 2 instead of powers of 10 since binary is base 2. For example, the binary number 1011.01 can be expressed as follows.

$$1011.01 = (1 \times 2^{3}) + (0 \times 2^{2}) + (1 \times 2^{1}) + (1 \times 2^{0}) + (0 \times 2^{-1}) + (1 \times 2^{-2})$$

$$= (1 \times 8) + (0 \times 4) + (1 \times 2) + (1 \times 1) + (0 \times \frac{1}{2}) + (1 \times \frac{1}{2})$$

$$= 11 \frac{1}{4}$$

You can include more bits to represent larger numbers or numbers with larger denominators.

#### 1.3.2 Octal and Hexadecimal Notations

Properly designed digital circuits can deal with large binary numbers fairly easily. For humans, however, long strings of 0s and 1s can become tedious and error-prone. Consider, for instance, the decimal number 927.625. We would express this in binary as 1110011111.101. To make it simpler for people to understand these numbers, we often use notations that combine several bits into one symbol. It is fairly easy to convert binary notation to another notation that is an exact power of 2, such as base 8 (octal) or base 16 (hexadecimal). It is much more complex to convert from binary to another base, such as base 5.

First, let's look at octal notation. This is base 8. It has eight symbols, 0 to 7. Since  $8 = 2^3$ , we can combine groups of three binary bits into single octal digits. The key is to start at the right place; that place is the radix point. (Think of this as the decimal point, but in any base/radix.) Going to the left, divide the binary bits into groups of three bits. If the final group has less than three bits, add leading zeroes to complete a group of three bits. Now do the same with the bits to the right of the radix point that represent the fractional portion of the number, grouping the bits into threes going right and adding trailing zeroes if needed to complete the final group. Figure 1.4 shows how we do this for our example value.

$$927.625 = 1110011111.101 = 001 110 011 111.101$$

= 1 6 3 7 . 5

Figure 1.4: Converting 927.625 from binary to octal. Zeroes added to complete groups of three bits are shown in red.

#### WATCH ANIMATED FIGURE 1.4

Hexadecimal is base 16. It has 16 symbols. We can use the decimal symbols 0 to 9 for ten of these symbols, but we still need six symbols for the values corresponding to 10 to 15. Hexadecimal uses the letters A to F for these values, with A=10, B=11, C=12, D=13, E=14, and F=15.

With that out of the way, we can use the same conversion process we used for octal, with one exception. Since  $16=2^4$ , we divide our binary number into groups of four bits instead of three. Figure 1.5 shows the conversion process for our example value.

```

927.625 = 1110011111.101 = 0011 1001 1111.1010

= 3 9 F . A

```

Figure 1.5: Converting 927.625 from binary to hexadecimal. Zeroes added to complete groups of four bits are shown in red.

#### WATCH ANIMATED FIGURE 1.5

#### 1.3.3 Converting from Decimal to Binary

There's one step I didn't cover explicitly yet: How did I get from 927.625 to 1110011111.101? You may have a calculator app that will do this automatically for you. If so, great, but put it away for a few minutes while we introduce the underlying process. We're actually going to have two separate processes, one for the integer part of the number and one for the fractional part.

First, let's look at the integer part. We divide  $927 \div 2$  to get a quotient of 463 and a remainder of 1. What we're really doing is expressing 927 as  $463 \times 2 + 1$ . Next, we divide 463 by 2 to get  $463 = 231 \times 2 + 1$ , or

$$927 = 463 \times 2 + 1 = (231 \times 2 + 1) \times 2 + 1 = 231 \times 4 + 1 \times 2 + 1$$

We continue this process until we're down to a final value of 0. The complete process for the integer portion is shown in Figure 1.6.

```

927 = 463 \times 2^{1} + 1 \times 2^{0}

927 ÷ 2 = 463 R 1

927 = (231 \times 2^{1} + 1) \times 2^{1} + 1 \times 2^{0} = 231 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

463 ÷ 2 = 231 R 1

927 = (115 \times 2^{1} + 1) \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} = 115 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

231 ÷ 2 = 115 R 1

927 = (57 \times 2^{1} + 1) \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} = 57 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

115 ÷ 2 = 57 R 1

927 = (28 \times 2^{1} + 1) \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0} = 28 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{1} + 1 \times 2^{0}

57 ÷ 2 = 28 R 1

927 = (14 \times 2^{1} + 0) \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

28 \div 2 = 14 R O

= 14 \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

927 = (7 \times 2^{1} + 0) \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

14 \div 2 = 7 R 0

=7\times2^{7}+0\times2^{6}+0\times2^{5}+1\times2^{4}+1\times2^{3}+1\times2^{2}+1\times2^{1}+1\times2^{0}

927 = (3 \times 2^{1} + 1) \times 2^{7} + 0 \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

7 \div 2 = 3R1

=3\times2^{8}+1\times2^{7}+0\times2^{6}+0\times2^{5}+1\times2^{4}+1\times2^{3}+1\times2^{2}+1\times2^{1}+1\times2^{0}

927 = (1 \times 2^{1} + 1) \times 2^{8} + 1 \times 2^{7} + 0 \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

3 ÷ 2 = 1 R 1

=1\times2^{9}+1\times2^{8}+1\times2^{7}+0\times2^{6}+0\times2^{5}+1\times2^{4}+1\times2^{3}+1\times2^{2}+1\times2^{1}+1\times2^{0}

927 = (0 \times 2^{1} + 1) \times 2^{9} + 1 \times 2^{8} + 1 \times 2^{7} + 0 \times 2^{6} + 0 \times 2^{5} + 1 \times 2^{4} + 1 \times 2^{3} + 1 \times 2^{2} + 1 \times 2^{1} + 1 \times 2^{0}

1 ÷ 2 = 0 R 1

=1\times2^9+1\times2^8+1\times2^7+0\times2^6+0\times2^5+1\times2^4+1\times2^3+1\times2^2+1\times2^1+1\times2^0

```

Figure 1.6: Conversion of decimal integer to binary

WATCH ANIMATED FIGURE 1.6

The remainders are combined to give us the binary representation of the integer. The first remainder is the least significant bit and the last remainder is the most significant bit. For our value of 927, this is 1110011111.

We calculate the fractional portion using a different but analogous approach. Instead of dividing by 2, we multiply by 2. The bits of the fraction in binary are the integer portion of each product. For our fraction of 0.625, we first multiply by 2 to get  $0.625 \times 2 = 1.25$ , or  $0.625 = 1.25 \times 2^{-1}$ . We keep the 1 and repeat the process on the remaining fractional value, 0.25, and continue until the remaining fraction is 0. (Sometimes a fraction would never end. For example, 1/3 = .010101... in binary. Normally we would decide how many bits to include in the fraction and round the result to that many bits.) Figure 1.7 shows this process for our fractional value.

```

\begin{array}{lll} 0.625 \times 2 = 1.25 & 0.625 = (1.25 \times 2^{-1}) = 1 \times 2^{-1} + .25 \times 2^{-1} \\ 0.25 & \times 2 = 0.50 & 0.625 = 1 \times 2^{-1} + (0.50 \times 2^{-1}) \times 2^{-1} = 1 \times 2^{-1} + 0 \times 2^{-2} + 0.5 \times 2^{-2} \\ 0.50 & \times 2 = 1.0 & 0.625 = 1 \times 2^{-1} + 0 \times 2^{-2} + (1.0 \times 2^{-2}) \times 2^{-1} = 1 \times 2^{-1} + 0 \times 2^{-2} + 1 \times 2^{-3} \end{array}

```

Figure 1.7: Conversion of decimal fraction to binary

#### WATCH ANIMATED FIGURE 1.7

Here, we combine the bits of the integer part of the product to generate the binary fraction. The first 1, generated by  $0.625 \times 2$ , is the most significant bit of the fraction. Unlike the integer procedure, which generated bits from least significant to most significant, the fraction procedure generates the bits in the opposite order, from most significant to least significant. It may help to describe this by saying that both procedures start by generating the bit closest to the radix point and move further away each iteration.

The final step is trivial. We simply concatenate the integer and fraction to produce the final result. For our example, this yields 927.625 = 1110011111.101.

As you might have guessed, you can use this process to convert a number from decimal (base ten) to any arbitrary base. Instead of dividing and multiplying by 2, we divide and multiply by the base we are converting to. Figure 1.8 shows this conversion from 927.625 in decimal to 12202.303 in base 5. Note that the fraction never terminates (it repeats as .303030...), so I chose to truncate it after three digits.

```

927 \div 5 = 185 R 2.625 \times 5 = 3.125185 \div 5 = 37 R 0.125 \times 5 = 0.62537 \div 5 = 7 R 2.625 \times 5 = 3.1257 \div 5 = 1 R 21 \div 5 = 0 R 1

```

Figure 1.8: Conversion of decimal number to base 5

#### **1.4 Numeric Formats**

Many digital systems, mostly computers, use several different numeric formats. In this section, we'll look at some of these formats. The first type, unsigned formats, is typically used for integers. In spite of its name, one unsigned format allows for both positive and negative numbers. We'll explain how this works shortly. Next, we'll examine signed formats, which differ from unsigned formats by as little as a single bit. Finally, we'll introduce floating point formats and the IEEE 754 floating point standard that is supported by virtually all computer systems.

#### 1.4.1 Unsigned Formats

There are two unsigned formats we discuss in this section. The first, traditional unsigned numbers, is simply the integer portion of the binary format we introduced in the previous section. Here, an n-bit number can take on any integer value from 0 to  $2^n$ -1. Figure 1.9 (a) shows the values for all 4-bit numbers in this format.