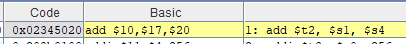

add $t2, $s1, $s4

- Looking at the sheet,

add:-

add rd, rs, rt -

R[rd] = R[rs] + R[rt] - OpCode/Funct 0/20

- R Type

-

- Looking further down, an R-Type has the following format:

Bits Usage 26-31 (6 bits) opcode 21-25 (5 bits) rs 16-20 (5 bits) rt 11-15 (5 bits) rd 6-10 (5 bits) shamt 0-5 (6 bits) funct

- What do you suppose this is used for?

- Take a look at the Figure 4.17, How do you suppose this is used?

- We may build a circuit to control the alu based on the funct code.

- And a signal from the Control unit.

- This is done in the book if you can't stand to wait.

OpCode 0 -> 000000

RS s1 (17) -> 10001 Careful here, the instruction and format do not match

RT s4 (20) -> 10100 Careful here, the instruction and format do not match

RD t2 (10) -> 01010 Careful here, the instruction and format do not match

SHAMT code as 0-> 00000

FNCT 20 -> 100000

000000 10001 10100 01010 00000 100000

00000010001101000101000000100000

0000 0010 0011 0100 0101 0000 0010 0000

0 2 3 4 5 0 2 0

0x02345020

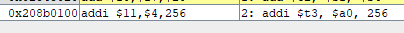

addi $t3, $a0, 256?

- Addi:

-

addi $rt, $rs, immediate -

R[rt] = R[rs] + SignExtImm- OpCode 8

- I type.

-

- This is an I type format

Bits Usage 26-31 (6 bits) opcode 21-25 (5 bits) rs 16-20 (5 bits) rt 0-15 (16 bits) immediate

-

OpCode 8 -> 001000 RS a0 (4) -> 00100 Careful here, the instruction and format do not match RT t3 (11) -> 0111 Careful here, the instruction and format do not match IMM 256 - 0000000100000000 001000 00100 01011 0000000100000000 00100000100010110000000100000000 0010 0000 1000 1011 0000 0001 0000 0000 2 0 8 B 0 1 0 0 0x208B0100 -

- Your choice, do you want to trace this through the ALU on Page 275? (Figure 4.15).

- What does

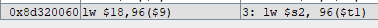

0x8d320060represent? - First note, all instruction formats start with a 6 bit opcode.

-

8d becomes 1000 1101 So the opcode is 1000 11 -> 10 00011 -> 23 - Looking on the back side of the green card, opcode corresponds to

lw - On the front side LW is an I type.

- two registers and an immediate

0x8d320060 - > 8 d 3 2 0 0 6 0 1000 1101 0011 0010 0000 0000 0110 0000 100011 01001 10010 0000000001100000 lw 9 18 96 opcode 10 0011 -> 23 -> lw RS -> 9 -> $t1 RT -> 18 -> $s2 96 -> 96 lw $s2, 96($t1) -